D2Audio D2-81431

D2Audio was a fabless semiconductor company founded around 2002 with a singular focus: closing the feedback loop on Class D amplification in the digital domain. Traditional Class D designs modulate an analog input into PWM, amplify it, and filter it back to analog — a process that introduces distortion at every stage boundary. D2Audio’s approach kept the signal digital from input to output stage, running adaptive correction algorithms against the actual PWM waveform and speaker current in real time. Intersil acquired D2Audio in 2009 for the IP portfolio. Renesas acquired Intersil in 2017. The D2-1 product family is now listed as Not Recommended for New Designs, which is the semiconductor industry’s way of saying the parts are still available but the engineering support is gone.

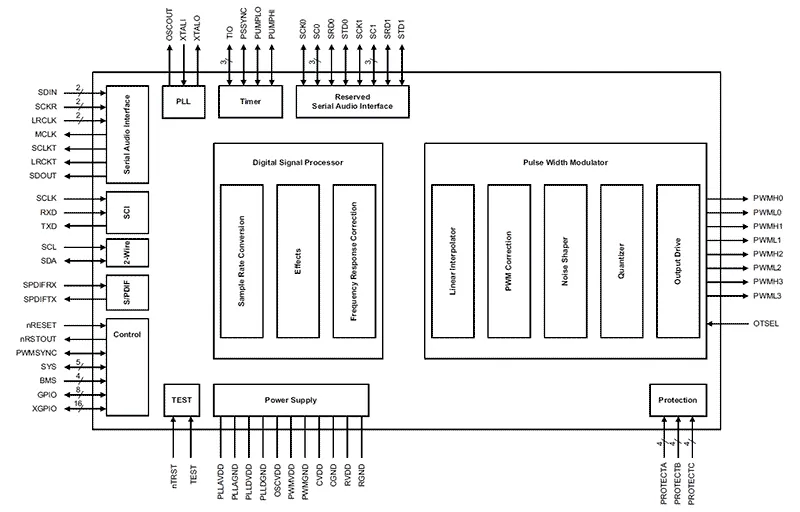

The D2-81431 is a member of the D2-1 family alongside the D2-81412, D2-81433, D2-81434, and D2-81435. It comes in a 128-pin LQFP package and runs its core logic at 1.7V to 1.9V. The part integrates a four-channel DSP with PWM controller, sample-rate converter, and a full suite of audio processing: parametric EQ, tone control, volume with soft ramp, dynamic range compression, crossover filters, and power limiting. It accepts up to four channels of I2S or left-justified digital audio at 16 to 24 bits, 32 to 192 kHz sample rates, with an optional S/PDIF input. Published specifications claim better than 110 dB signal-to-noise ratio and less than 0.1% THD+N across the audio band.

The distinguishing feature of the D2-1 architecture is the adaptive digital feedback system. The DSP monitors both the PWM output voltage and the speaker return current through dedicated sense inputs, then applies correction on a cycle-by-cycle basis. This is not a simple open-loop design where you set coefficients and hope the output stage behaves — the DSP actively measures what is actually happening at the speaker terminals and adjusts its modulation to compensate for power supply droop, thermal drift in the MOSFETs, and nonlinearity in the output filter. D2Audio’s published application data shows this feedback loop pulling measured THD+N down to approximately 0.05% under load, a substantial improvement over the raw open-loop figure.

The D2-81431 has no internal non-volatile memory. It boots entirely from an external I2C EEPROM connected through a dedicated bus on GPIO6 and GPIO7. This NVM bus is separate from the host control I2C interface (SCL/SDA) that the system controller uses for runtime parameter writes. At power-on, the boot mode is determined by the BMS[3:0] pin strapping — four pins whose logic levels at reset select one of several boot sources and protocols.

Boot mode table

Section titled “Boot mode table”The D2-1 Family Audio SOC Datasheet (Table 2) defines the complete set of boot modes. The modes relevant to this amplifier:

| Mode | BMS[3:0] | Role | Speed | Description |

|---|---|---|---|---|

| 1 | 0001 | Master | 400 kb/s | I2C ROM on 2-wire port 0 (SCL0/SDA0) |

| 7 | 0111 | Master | 384 kb/s | I2C ROM on GPIO port (SCL=GPIO7, SDA=GPIO6) |

| C | 1100 | Slave | per master | I2C slave boot from host MCU, address 0x44 |

| 2 | 0010 | Slave | 384 kb/s | Fast async SCI slave boot (chip-to-chip) |

| 3 | 0011 | Slave | per master | SPI slave boot |

In this amplifier, the UPDATE/OPERATE switch on the rear panel physically changes the BMS[3:0] pin strapping on the D2-81431:

-

OPERATE mode uses Boot Mode 7 (BMS=0111): the D2-81431 acts as I2C master at 384 kb/s, autonomously reading its entire firmware image from the AT24C512 EEPROM via GPIO6 (SDA) and GPIO7 (SCL). This is the private NVM bus, separate from the host control bus.

-

UPDATE mode uses Boot Mode C (BMS=1100): the D2-81431 becomes an I2C slave at address 0x44 (0b1000100x). The LPC2103F acts as I2C master, pushing firmware data into the D2-81431’s internal RAM. The boot ROM in the D2-81431 then writes that data through to the EEPROM via GPIO6/GPIO7.

Boot timing from the datasheet: after nRESET deassertion, the EEPROM boot sequence begins after tEEboot = 2.65 ms, and the external boot source must be ready within tEXTbootRDY = 2.4 ms.

Runtime control

Section titled “Runtime control”During normal operation, the host MCU communicates with the D2-81431 at I2C address 0xB2. Writes to this address modify runtime parameters: volume level, EQ coefficients, crossover frequency, phase offset, compression thresholds. The D2-81431 applies these changes in real time without interrupting audio output.

Audio Canvas III

Section titled “Audio Canvas III”The OEM development environment for the D2-1 family was a Windows application called “Audio Canvas III,” also referred to as the “D2 Audio Customization GUI v3.” Details gathered from blog posts, forum threads, and surviving Renesas documentation:

- Architecture: Java with Swing/AWT GUI, Motorola 56300 assembly for DSP code generation, Octave for DSP research and development

- Audio blocks library: Volume, Parametric EQ, Biquad Filters, Crossover (Linkwitz-Riley/Butterworth/Bessel), Compressor, Excursion Control, Delay, RMS Level Meter

- Dynamic register addressing: Register addresses are assigned dynamically per build, not fixed. This is why no published register map exists for the D2-1 family — every OEM product has a unique memory layout generated by Audio Canvas

- Project persistence: Encrypted XML files (the encryption is on the PC-side design files, not the EEPROM images)

Audio Canvas III was never a public tool. D2Audio, Intersil, and Renesas distributed it only to licensed OEM customers under NDA with volume purchase agreements. The diyAudio community has threads spanning years of people unsuccessfully trying to obtain it. Intersil’s stated position was that “support for new generation of ICs is for big customers.” Renesas’s product page for the D2-1 family offers only two datasheets — no tools, no application software.

The firmware images Audio Canvas produces are proprietary binary blobs specific to each OEM’s amplifier design. There is no generic “D2-81431 firmware” — every product that uses this chip has its own custom image built from the OEM’s Audio Canvas project.